Le calcul haute performance s’est imposé comme un enjeu de souveraineté. Entre IA, climat et défense, l’Europe ne peut plus dépendre uniquement de puces américaines ou asiatiques. SiPearl arrive avec Rhea, un microprocesseur HPC pensé pour l’ère exascale et pour réduire la dépendance, sans sacrifier la performance.

| Habitué au story des 15 secondes ? Voilà ce que tu dois retenir : ⚡ |

|---|

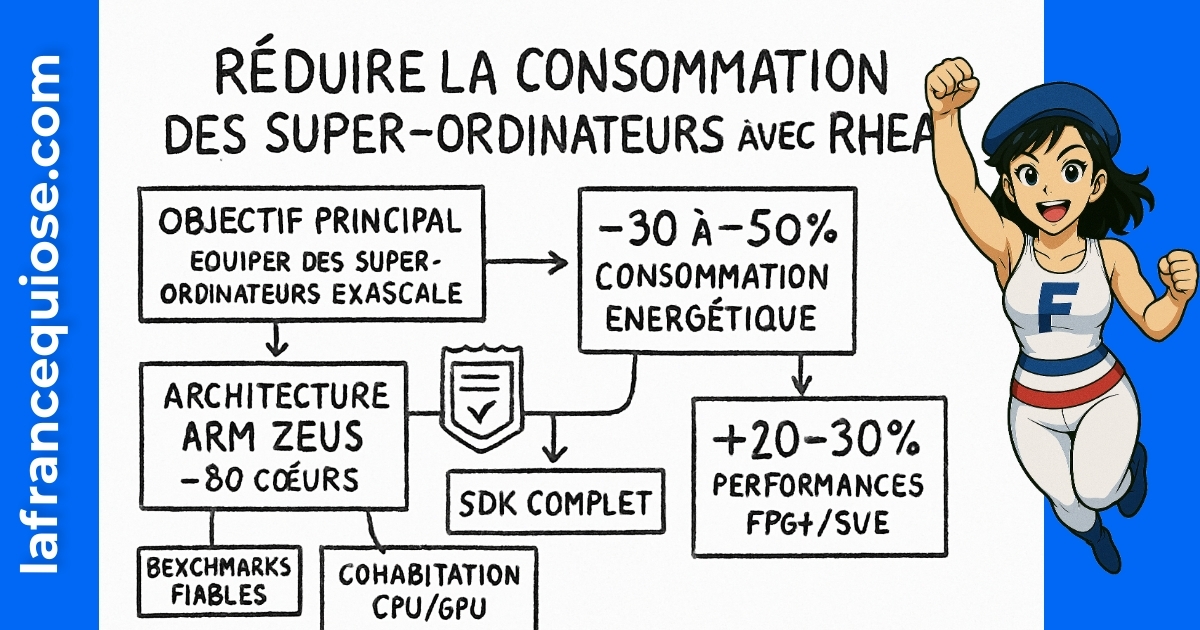

| ✅ Objectif : Rhea veut équiper des supercalculateurs européens exascale tout en coupant la facture énergétique de moitié 🔋 |

| ✅ Architecture : cœurs Arm Neoverse V1 (« Zeus »), interopérable avec GPU/IA (AMD, Intel, NVIDIA, Graphcore) 🧠 |

| ✅ Urgence : publier des benchmarks SVE/FP64, PCIe, scaling thermique pour convaincre les centres HPC 🧪 |

| ✅ Stratégie : s’appuyer sur EuroHPC/EPI, l’écosystème Atos/Eviden, ParTec, CEA, STMicroelectronics, Thales, Airbus, Menta 🧩 |

Exascale, souveraineté et réalité terrain: où le CPU Rhea de SiPearl peut faire la différence

La course à l’exascale n’est pas un concours de fiches techniques, c’est un choix stratégique. Les supercalculateurs pilotent la recherche médicale, la simulation climatique, la sécurité et le cœur de l’IA. Tant que l’Europe n’a pas son microprocesseur de référence, la dépendance technologique reste une vulnérabilité. SiPearl positionne Rhea comme un CPU HPC à haute efficacité énergétique, compatible avec les accélérateurs déjà dominants.

Le contexte joue en faveur de cette ambition. EuroHPC structure un écosystème, mais la maturité industrielle reste à construire. Les acteurs américains et asiatiques cumulent des années d’optimisation, du compilateur aux bibliothèques mathématiques. S’imposer exige une différenciation nette: performance par watt, interopérabilité, coûts maîtrisés, ecosystème logiciel prêt pour production.

Les centres HPC veulent des preuves, pas des promesses. Les métriques qui comptent: débit FP64 avec SVE, latence mémoire sous pression HBM/DDR5, scaling multi-socket, profil thermique par charge et stabilité avec SLURM/containers. C’est la check-list qui conditionne une adoption, indépendamment des discours de souveraineté.

Cas d’usage: ce que les clients européens attendent vraiment

Un centre comme le CEA ne choisit pas sur la com’ mais sur les jobs réels: mécanique des fluides, sismologie, IA scientifique. Un industriel comme Airbus regarde la précision et le temps de cycle des simulations CFD. Thales scrute la robustesse en environnements sensibles. L’intégrateur Atos/Eviden (héritier de Bull) et un orchestrateur comme ParTec exigent une compatibilité sans friction avec les GPU et les réseaux haute performance.

Dans ce cadre, la promesse Rhea a trois atouts. D’abord, une base Arm Neoverse V1 connue, rassurante pour porter les toolchains. Ensuite, un design pensé pour s’accrocher à des accélérateurs variés, du GPU classique à des puces Graphcore spécialisées. Enfin, un angle “éco-efficace” pertinent quand l’électricité devient une ligne majeure du TCO.

- 🚀 Priorité n°1: publier des benchmarks FP64/SVE comparables, reproductibles, signés par des labos indépendants (ex.: CEA, universités) ;

- 🔌 Priorité n°2: prouver la cohabitation CPU-GPU sans goulots d’étranglement (PCIe, cohérence mémoire, pile logicielle) ;

- 🌡️ Priorité n°3: documenter le profil thermique par charge (IA, CFD, FEA) avec courbes de fréquence et consommation ;

- 🧰 Priorité n°4: livrer un SDK opérationnel (compilateurs, BLAS, FFT, MPI, profilers, conteneurs) avec recettes prêtes à l’emploi ;

- 🏷️ Priorité n°5: proposer un pricing clair par nœud et par rack, TCO sur 3–5 ans et support premium.

Exemple pratique: Nadia, directrice d’un centre HPC universitaire, doit valider un nouveau cluster pour l’IA climatique. Elle comparera le coût par modèle entraîné, la consommation énergétique par époque, la stabilité sur 30 jours de job. Sans métriques ouvertes, le choix restera conservateur.

Pour accélérer l’adoption, exploite des ressources concrètes sur la stratégie produit et l’automatisation: un retour d’expérience sur la scalabilité et l’outsourcing malin peut s’inspirer de cette lecture utile sur l’effet “marketplace” façon Bezos. Et pour la montée en compétence rapide des équipes techniques, ce guide pour acquérir une skill en 30 jours fait gagner des mois.

Architecture Arm Neoverse V1, interop GPU/IA et efficacité énergétique: comment intégrer Rhea sans casser la prod

La crédibilité se joue dans le détail. Rhea s’appuie sur Arm Neoverse V1 (surnommé « Zeus »), une architecture taillée pour la bande passante mémoire et le vectoriel SVE. Lors des annonces techniques, plusieurs éléments clés se sont dessinés: jusqu’à ~80 cœurs Neoverse V1, HBM pour le débit, DDR5 pour la capacité, et une plate-forme ouverte pour les accélérateurs IA et GPU. Sur le papier, c’est le combo idéal pour les codes multi-physiques et l’IA hybride.

La valeur n’apparaît que si l’intégration est fluide. Les centres HPC veulent brancher des GPU NVIDIA, AMD ou des accélérateurs Graphcore sans réécrire la moitié de leur stack. Ça signifie une pile PCIe récente, une topologie pensée pour limiter les hops, et des drivers matures. Côté logiciel, l’alignement sur MPI, OpenMP, OpenACC, les conteneurs (Apptainer/Docker), et l’orchestration SLURM est non négociable.

Mode opératoire: ce que doit livrer un “kit d’intégration Rhea”

Un « kit » gagnant se repère à ses raccourcis opérationnels. Les ingénieurs veulent cloner un repo, lancer un script, et obtenir des courbes propres pour décision. Pas de mystère, un parcours type doit couvrir le chemin du code au rack, sans friction.

- 🧪 Bench repos: scripts pour HPL, HPCG, SPEChpc, miniapps (miniFE, AMG), benchmarks FP64 SVE ;

- 📦 Conteneurs: images optimisées (BLAS/FFT/MPI) pour Arm avec profils énergie ;

- 🔗 Interop: recettes GPU/IA (CUDA/HIP/oneAPI, Poplar pour Graphcore) avec latences PCIe/NUMA ;

- 🧭 Guides: best practices topologie, pinning CPU, hugepages, I/O ;

- 📈 Dashboards: Grafana/Prometheus pour conso, fréquence, température, throttling.

Illustration terrain: un cluster « mixte » monté par un intégrateur type Atos/Eviden ou ParTec. Le cœur CPU Rhea pilote la simulation, un pool GPU traite l’IA, le tout branché à un réseau HDR/NDR. Le succès dépend d’un goulot unique: l’orchestration et la gestion mémoire. Si les notebooks ML et les pipelines CFD tournent sans tuning excessif, le pari est gagné.

Pour renforcer la culture produit et la clarté de ta roadmap, inspire-toi de ce retour d’expérience sur des intégrations data/IA réalistes. Et si la voix IA t’intéresse pour l’accessibilité des docs et démos, jette un œil aux travaux de Kyutai et Unmute, pertinents pour concevoir des supports audio interactifs.

Dernier point: l’efficacité énergétique. Les promesses de division par deux de la consommation à puissance équivalente séduisent. La crédibilité passera par des tests normalisés (joules par job, perfs par watt), et une traçabilité depuis le PDU. Sans ça, le gain restera théorique.

Chaîne de valeur européenne: fabless, dépendance TSMC et leviers pour sécuriser la production

La structure fabless de SiPearl accélère la conception mais expose à un risque bien connu: la dépendance au fondeur, ici TSMC. Les tensions d’approvisionnement peuvent affecter les plannings, les coûts et les volumes. Le remède n’est pas magique, mais une stratégie « multi-leviers » s’impose pour réduire le risque et gagner en résilience.

Premier levier: l’industrialisation européenne autour du packaging, des tests et de l’assemblage. Les capacités locales existent pour le post-silicon, couplées à l’expertise du CEA et de STMicroelectronics (FD-SOI, packaging avancé, caractérisation). Deuxième levier: des accords anticipés sur la mémoire HBM, la DDR5 et les interconnexions, afin de sécuriser l’ensemble du bill of materials. Troisième levier: explorer des architectures chiplet et l’intégration d’IP eFPGA (Menta) pour gagner en agilité produit sans re-taper une full mask set à chaque itération.

Partenaires et cas d’école: du design au déploiement

La filière européenne a déjà des piliers. Atos/Eviden (héritier de Bull) et ParTec intègrent des supercalculateurs clé en main. CEA et les universités pilotent la R&D et les validations. Thales et Airbus amènent des cas d’usage critiques qui poussent la roadmap. STMicroelectronics met à disposition des briques industrielles et de l’expertise packaging. L’écosystème se tient, à condition de synchroniser les roadmaps et d’outiller les transferts technos.

Scénario type: un lot de puces Rhea sort du fondeur. La qualification électrique s’enchaîne, puis la validation logicielle sur une plateforme de pré-série. En parallèle, un « design partner » défense teste un pipeline crypto et un modèle radar, pendant qu’un acteur aéronautique valide la CFD avec ses solveurs historiques. À la clé, des ajustements micrologiciels, parfois une révision stepping, avant production volume. C’est ce parcours que les acheteurs veulent voir cadré, avec jalons et responsabilités.

- 🛡️ Risque: goulots d’étranglement d’approvisionnement → Action: contrats long terme, buffers, packaging européen ;

- 🔁 Risque: révisions silicium tardives → Action: prototypage rapide, Menta eFPGA pour patchs logiques ;

- 🌍 Risque: dépendance unique à TSMC → Action: plan B sur nœuds alternatifs et focus post-silicon UE ;

- 🏗️ Risque: intégration rack instable → Action: kits validés avec Atos/Eviden, ParTec, tests réseau et stockage ;

- 📜 Risque: conformité et support → Action: SLA européens, certifications sectorielles.

Envie de creuser la stratégie d’exécution et l’effet réseau dans les écosystèmes tech? Ce décryptage sur la méthode Bezos s’applique aussi aux plateformes HPC: simplifier, standardiser, scaler.

Gouvernance, financements et feuille de route: ce que les décideurs doivent exiger avant fin 2025

SiPearl n’est pas un projet solitaire. La gouvernance mêle vision et exécution avec une équipe pluridisciplinaire. Côté direction: Philippe Notton pilote la stratégie ; Laure Perfetti structure les talents ; Ying-Chih Yang porte la direction technique ; Gaël Paul orchestre l’ingénierie ; Vivian Blanchard accélère la R&D hardware ; Vincent Casillas couvre la R&D software et système. Sur les partenariats et le go-to-market, Christophe Ménard et Craig Prunty posent le positionnement ; Anna Riverola pilote l’international et la recherche ; Matteo Tonelli ancre l’Italie. Côté finances, Jean-Luc Gilbert sécurise investisseurs et trésorerie, Cornelia Emmerlich verrouille la gouvernance juridique.

Le financement suit la montée en puissance. Une Série A s’est structurée en plusieurs temps: une première clôture autour de 90 M€ (avec Arm, Atos/Eviden, EIC Fund, French Tech Souveraineté, BEI), puis un closing définitif porté à environ 130 M€, incluant de nouveaux tickets et complété par des subventions européennes et françaises. C’est sérieux, mais pour jouer à l’échelle des géants du HPC et de l’IA, la marche de financement suivante reste déterminante.

Jalons critiques à exiger pour sécuriser les déploiements

Les acheteurs publics et privés doivent conditionner leurs commandes à des jalons vérifiables. C’est sain, et cela accélère la maturité produit. L’objectif n’est pas le “moonshot”, mais un trajet maîtrisé vers la production stable.

- 📊 Benchmarks publiés: FP64 (SVE), HPL/HPCG, miniapps, perfs/watt, reproductibles par un tiers ;

- 🧩 Interop validée: GPU (NVIDIA/AMD), IA (oneAPI/CUDA/HIP, Graphcore), réseau (Infiniband/Ethernet haut débit) ;

- 🛠️ SDK complet: toolchains, bibliothèques optimisées, profilers, images conteneurisées ;

- 📦 GA matérielle: stepping figé, errata publics, disponibilité racks via Atos/Eviden, ParTec ;

- 👥 Support: équipe d’intégration et customer success dédiée pour les 100 premiers clients.

L’ambition de montée en charge (de ~130 à potentiellement 1000 collaborateurs) devra être confirmée par des recrutements ciblés: validation, performance engineering, sécurité, et devrel. Les centres pilotes (CEA, universités, partenaires industriels) sont le meilleur terrain pour itérer vite et bien.

Tu veux suivre ces jalons sans te perdre? Ajoute un rituel d’apprentissage dans tes équipes: un sprint de 30 jours, un livrable, une compétence validée. Ce process est détaillé ici: 30 jours, une skill, un impact. Et garde en favori la home pour d’autres analyses sans langue de bois: La France Qui Ose.

| 📌 KPI clé | 🎯 Cible réaliste | 🧪 Mode de preuve |

|---|---|---|

| Perfs FP64/SVE | +20–30% vs références Arm comparables ⚙️ | HPL/HPCG signés par un labo 🇪🇺 |

| Perfs/Watt | -30 à -50% conso à perf égale 🔋 | Mesures rack-to-PDU, dashboards |

| Interop GPU/IA | Compatibilité NVIDIA/AMD/Graphcore ✅ | Suites CUDA/HIP/oneAPI, latences PCIe |

| Stabilité | 30 jours sans incident majeur 🧱 | Logs SLURM, SLO validés |

| Disponibilité | Lead time < 16 semaines 📦 | Contrats intégrateurs (Atos/Eviden, ParTec) |

Business, SEO technique et go-to-market: comment bâtir un écosystème autour d’un CPU souverain

Un processeur ne gagne pas seul. Il lui faut des outils, des guides, des histoires. Les ISV (éditeurs logiciels), les laboratoires et les intégrateurs veulent des exemples concrets, des “cookbooks” prêts à lancer, des numéros de téléphone quand ça bloque. L’angle business compte autant que le silicon.

Commence par baliser les parcours. Un portail développeur clair, docs “task first” (ex.: “accélérer une FFT double précision sur Rhea + GPU”), et une bibliothèque de cas d’usage: CFD aéronautique (intérêt pour Airbus), crypto et radar (intérêt pour Thales), IA scientifique (intérêt pour hôpitaux et climat). Ajoute des quick wins: scripts de portage Fortran/C++ vers Arm, recettes SVE, profils énergie.

Playbook actionnable pour l’adoption développeurs et décideurs

Les contenus qui performent mixent pédagogie et preuve. Des articles techniques bien référencés, une série vidéo, et des webinaires avec questions sans filtre. Pas de jargon creux: des chiffres, des commits, des retours d’expérience.

- 📚 Documentation: pages “start here”, snippets, erreurs fréquentes et fix ;

- 🎥 Vidéos: démos courtes “du code au résultat” ;

- 🧭 Guides orientés décision: TCO, SLA, roadmap, compatibilité ;

- 🤝 Community: forum, Slack/Discourse, office hours avec ingénieurs ;

- 🔎 SEO technique: schémas, glossaire, maillage interne vers études et benchmarks.

Pour la partie éditoriale et l’audience, inspire-toi des méthodes “sans poudre aux yeux” qu’on analyse régulièrement. Un exemple? Cette note sur des intégrations IA pragmatiques évite les buzzwords et ramène au terrain. Autre levier: bâtir une stratégie “voix” pour démos et support, point développé ici avec Kyutai/Unmute.

Sur le plan partenariats, rapproche des acteurs clés: Atos/Eviden et ParTec pour la mise en rack, CEA pour la validation scientifique, STMicroelectronics et Menta pour l’IP et le packaging, Thales et Airbus pour les pilotes industriels. La boucle marché-produit est alors continue: besoin → test → patch → déploiement.

Besoin d’un framework simple pour structurer ton calendrier et habituer les équipes à délivrer? Ce guide “30 jours, une skill” donne une cadence robuste. Et si l’effet plateforme te parle, la réflexion “Bezos” l’illustre bien: focus sur les interfaces, obsédé par la mesure.

Enfin, surveille les signaux faibles: contributions open-source sur les bibliothèques mathématiques, tickets fermés dans les compilos, retours d’intégrateurs. Les projets HPC gagnent au mètre, pas au sprint. L’écosystème qui documente, répond et livre finit par emporter les appels d’offres.

Questions fréquentes

Rhea est-il juste un Arm Neoverse “repackagé” ?

Non. La base Arm Neoverse V1 est assumée, mais l’intérêt vient des choix d’architecture (HBM + DDR5, interop GPU/IA, optimisations SVE) et de la cible HPC. La preuve passera par des benchmarks ouverts et des intégrations validées en production.

Quels sont les partenaires clés autour de SiPearl pour industrialiser ?

Atos/Eviden (héritier de Bull) et ParTec pour l’intégration, CEA pour la validation, STMicroelectronics et Menta pour l’IP/packaging, ainsi que des liens avec les écosystèmes GPU/IA (NVIDIA, AMD, Graphcore).

Quid de la dépendance à TSMC ?

C’est le talon d’Achille des modèles fabless. Les parades: sécurisation des capacités, packaging et test en Europe, buffers de composants critiques, et exploration chiplet pour accélérer les révisions.

Quels KPIs regarder pour décider un achat Rhea ?

Perfs FP64/SVE (HPL/HPCG), perfs par watt, latences PCIe/NUMA, stabilité 30 jours, compatibilité GPU/IA, lead time et SLA intégrateurs.

Comment les équipes techniques peuvent-elles monter en compétence rapidement ?

Mettre en place un rituel d’apprentissage de 30 jours avec livrables mesurables. Guide recommandé: Apprendre une skill en 30 jours. Pour rester au fait des avancées IA/HPC, garde en favori La France Qui Ose.

Moi c’est Mariane (avec un seul “n”).

J’ai troqué les process corporate contre des contenus qui claquent (et qui rankent).

Passionnée par le business en ligne, le SEO et l’IA, je transforme les idées floues en stratégies digitales qui font du bruit là où ça compte : dans les résultats. Je crois qu’avec un peu de tech, beaucoup d’audace, et une bonne dose de clarté, on peut faire exploser bien plus que des KPI.